THIS SECTION IS UNDER CONSTRUCTION

Видеоконтроллер

Video Adapter в текстовом режиме:

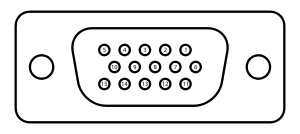

VGA 15-pin (VGA = Video Graphic Array) --------------------------------------------------------------- pin name description alt. description --------------------------------------------------------------- 1 RED Red video 2 GREEN Green video 3 BLUE Blue video 4 N/C Monitor ID (2) 5 GND Ground (HSync) Ground 6 RED_RTN Red return Red Ground 7 GREEN_RTN Green Return Green Ground 8 BLUE_RTN Blue Return Blue Ground 9 +5V +5V (DDC) [KEY] 10 GND Ground (VSync, DDC) Sync Ground 11 N/C Monitor ID (1) 12 SDA I2C DDC data Monitor ID (0) 13 HSYNC Horizontal Sync 14 VSYNC Vertical Sync 15 SCL I2C DDC clock N/C --------------------------------------------------------------- DDC1 = Unidirectional DDC2 = Bidirectional

Более старый вариант 9-pin ---------------------------------- pin name description ---------------------------------- 1 RED Red Video 2 GREEN Green Video 3 BLUE Blue Video 4 HSYNC Horizontal Sync 5 VSYNC Vertical Sync 6 RGND Red Ground 7 GGND Green Ground 8 BGND Blue Ground 9 SGND Sync Ground ----------------------------------

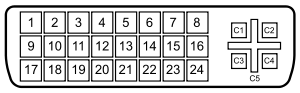

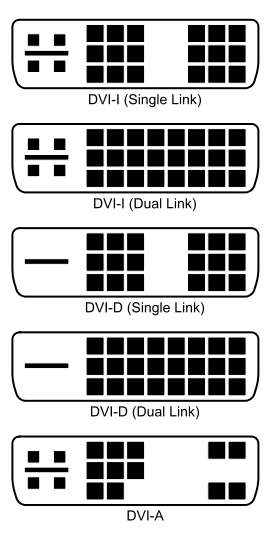

--------------------------------------------------- pin description --------------------------------------------------- 1 TMDS Data 2- Digital Red- (1) 2 TMDS Data 2+ Digital Red+ (1) 3 TMDS Data 2/4 shield 4 TMDS Data 4- Digital Green- (2) 5 TMDS Data 4+ Digital Green+ (2) 6 DDC Clock 7 DDC Data 8 Analog VSYNC 9 TMDS Data 1- Digital Green- (1) 10 TMDS Data 1+ Digital Green+ (1) 11 TMDS Data 1/3 shield 12 TMDS Data 3- Digital Blue- (2) 13 TMDS Data 3+ Digital Blue+ (2) 14 +5V (power for monitor snandby) 15 GND (for pin14 and analog sync) 16 Hot plug detect 17 TMDS Data 0- Digital Blue- (1) 18 TMDS Data 0+ Digital Blue+ (1) 19 TMDS Data 0/5 shield 20 TMDS Data 5- Digital Red- (2) 21 TMDS Data 5+ Digital Red+ (2) 22 TMDS clock shield 23 TMDS clock+ Digital clock+ 24 TMDS clock- Digital clock- C1 Analog Red C2 Analog Green C3 Analog Blue C4 Analog HSYNC C5 Analog Ground (for Red, Green, Blue) --------------------------------------------------- TMDS = Transaction Minimized Differental Signaling non-standart form of 8B/10B encoding

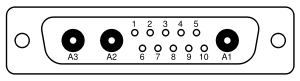

DB13W3 --------------------------------------------------- pin Description:Sun Description:SGI --------------------------------------------------- 1 GND Monitor ID 3/SCL 2 VSYNC Monitor ID 0/SDA 3 Sense 2 Composite Sync 4 Sense ground HSYNC 5 Composite sync VSYNC 6 HSYNC Monitor ID 1/DDC +5V 7 GND Monitor ID 2/DDC ground 8 Sense 1 Ground 9 Sense 0 Ground 10 Composite gnd Sync Ground A1 Red Red A2 Green Green Gray for monochrome A3 Blue Blue ---------------------------------------------------

Composite 1 + 2 -

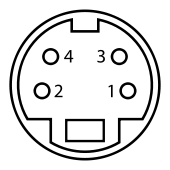

S-Video ------------------------------------- pin description ------------------------------------- 1 Ground (Y) 2 Ground (C) 3 Y Intency (Lumminance) 4 C Color (Chrominance) -------------------------------------

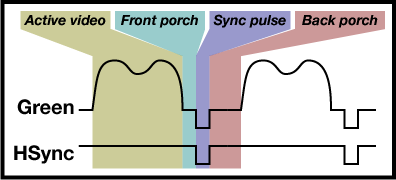

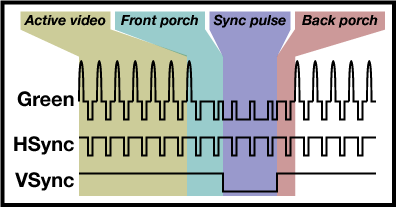

VGA Timing -------------------------------------------------------------------- Pixel Horizontal (in pixels) Vertical (in lines) Clock Active Front Sync Back Active Front Sync Back Format MHz Video Porch Pulse Porch Video Porch Pulse Porch -------------------------------------------------------------------- 640x480 60Hz 25.175 640 16 96 48 480 11 2 31 640x480 72Hz 31.500 640 24 40 128 480 9 3 28 640x480 75Hz 31.500 640 16 96 48 480 11 2 32 640x480 85Hz 36.000 640 32 48 112 480 1 3 25 800x600 56Hz 38.100 800 32 128 128 600 1 4 14 800x600 60Hz 40.000 800 40 128 88 600 1 4 23 800x600 72Hz 50.000 800 56 120 64 600 37 6 23 800x600 75Hz 49.500 800 16 80 160 600 1 2 21 800x600 85Hz 56.250 800 32 64 152 600 1 3 27 1024x768 60Hz 65.000 1024 24 136 160 768 3 6 29 1024x768 70Hz 75.000 1024 24 136 144 768 3 6 29 1024x768 75Hz 78.750 1024 16 96 176 768 1 3 28 1024x768 85Hz 94.500 1024 48 96 208 768 1 3 36 --------------------------------------------------------------------

Блок-схема адаптера типа VGA:

Library ieee; Use ieee.std_logic_1164.all; Entity vga is Port ( Clk : IN std_logic; Nrst : IN std_logic; Hsync : OUT std_logic; Vsync : OUT std_logic; Red : OUT std_logic_vector (1 downto 0); Green : OUT std_logic_vector (1 downto 0); Blue : OUT std_logic_vector (1 downto 0); Address : OUT (std_logic_vector (15 downto 0); Data : IN (std_logic_vector (7 downto 0); RAM_en : OUT std_logic; RAM_oe : OUT std_logic; RAM_wr : OUT std_logic ); End entity vga; Architecture core of vga is -- VGA internal signals go here Begin -- VGA Interface core goes here End architecture core; Mem_read : process ( pclk, nrst ) is signal current_address : unsigned (16 downto 0); Begin If nrst = '0' then Pixelcount <= 0; Current_address <= 0; Else If rising_edge(pclk) then Current_address <= current_address + 1; Address <= std_logic_vector(current_address); Pixel_data <= data; End if; End if; End process; signal pixel_data : std_logic_vector ( 7 downto 0 ); Hsync_counter : process ( clk, nrst ) is Hcount : unsigned ( 11 downto 0 ); Begin If nrst = '0' then Hcount <= 0; Hsync <= '1'; Else If hcount > and hcount < 2988 then hsync <= '0'; else hsync <= '1'; End if; If hcount < 3177 then Hcount <= hcount + 1; Else Hcount <= 0; End if; End if; End process; Clk_div : process ( clk, nrst ) is Begin If nrst = '0' then Count <= 0; Vclk <= '0'; Else If count = 1999 then Count <= 0; Vclk <= not vclk; Else Count <= count + 1; End if; End if; End process; Vsync_timing : process (vclk) is Begin If nrst = '0' then Vcount <= 0; Else If vcount>15700 and vcount < 15764 then Vsync <= '0'; Else Vsync <= '1'; End if; If vcount > 16784 then Vcount <= 0; Else Vcount <= vcount + 1; End if; End if; End process; Hblank_counter : process ( clk, nrst ) is Hcount : unsigned ( 11 downto 0 ); Begin If nrst = '0' then Hcount <= 0; hblank <= '1'; Else if hcount > 2517 and hcount < 3177 then hblank <= '0'; else hblank <= '1'; End if; If hcount < 3177 then Hcount <= hcount + 1; Else Hcount <= 0; End if; End if; End process; Vblank_timing : process (vclk) is Begin If nrst = '0' then Vcount <= 0; Vblank<='1'; Else If vcount > 15250 and vcount < 16784 then vblank <= '0'; Else vblank <= '1'; End if; If vcount > 16784 then Vblank <= 0; Else Vcount <= vcount + 1; End if; End if; End process; Pixel_handler : process (pclk) is Begin Red <= data(1 downto 0); Green <= data(3 downto 2); Blue <= data(5 downto 4); End process; Pixel_handler : process (pclk) is Blank : std_logic_vector (1 downto 0); Begin Blank(0) <= hblank or vblank; Blank(1) <= hblank or vblank; Red <= data(1 downto 0) & blank; Green <= data(3 downto 2) & blank; Blue <= data(5 downto 4) & blank; End process;

Типичные регистры CRT контроллера (CGA): 00 Horizontal Total Register (Число знако-мест на одной линии сканирования, включая обратный ход луча) 01 Horizontal Display Enable End Register 02 Horyzontal Sync Position 03 Horyzontal Sync Pulse Width 04 Vertical Raws 05 Vertical Total Adjust 06 Vertical Displayed 07 Vertical Sync Position (начало обратного хода луча) 08 Interlase Mode Register 09 Max Scan-line register 0A Cursor Start register 0B Cursor End register 0C,0D Start Address of Video Memory 0E,0F Cursor Location register

GPU

CRT controller. Видео-интерфейсы

Монитор

CRT монитор

CRT (Cathode Ray Tube)

LCD монитор

Активная матрица:

Особенности размещения:

Электронные чернила